To get started with FPGA (at home) you need to know how to infer logic with a hardware description language (HDL) and how to use specialist tools to convert the HDL code into a netlist (initially) and then a design laid out on the FPGA fabric. There are a number of good VHDL tutorial websites already in existence, so I'm not going to try and replicate them here, only reference them. There are also free tools for download that you can use for your self-taught introduction to FPGA.

- FPGA Design Process

- Tool Installation

- Suggested Vivado Installation Options

- Learning VHDL

- Tutorials

- Suggested Steps

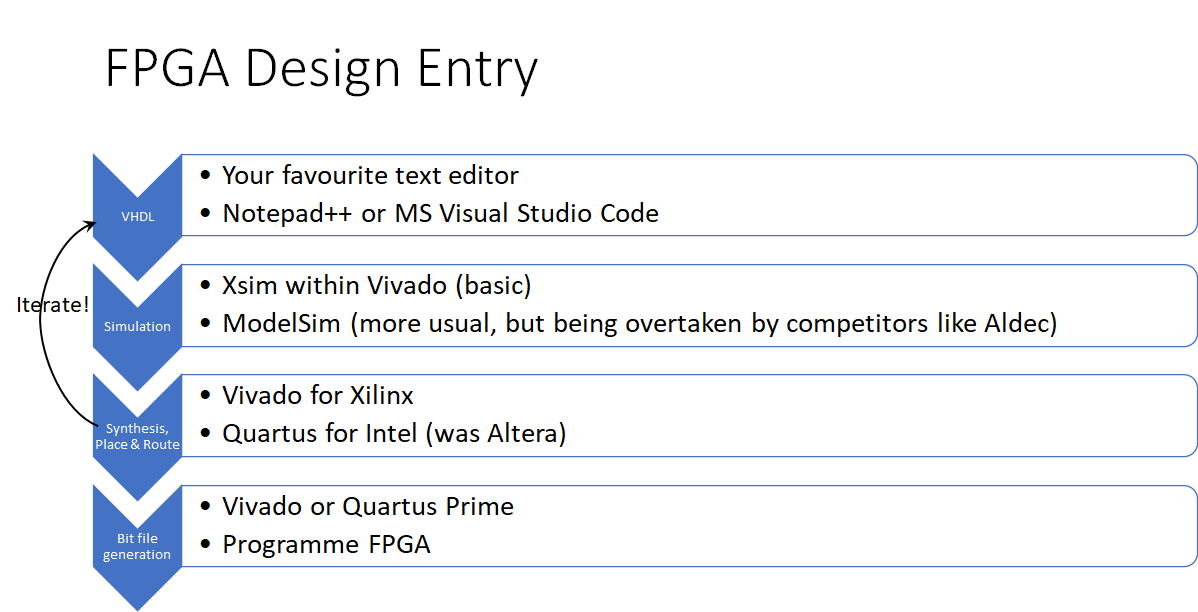

FPGA Design Process

Here's the basic design flow for FPGA, illustrated with tool vendors. I'll stick to just two FPGA manufactures due to my personal familiarity with them. My apologies if you are from one of the other perfectly good FPGA options around. The "iterate" loop is for when you don't meet timing, typically setup time as the logic between registers is too bloated, or for sorting out clock domain crossing oversights etc.

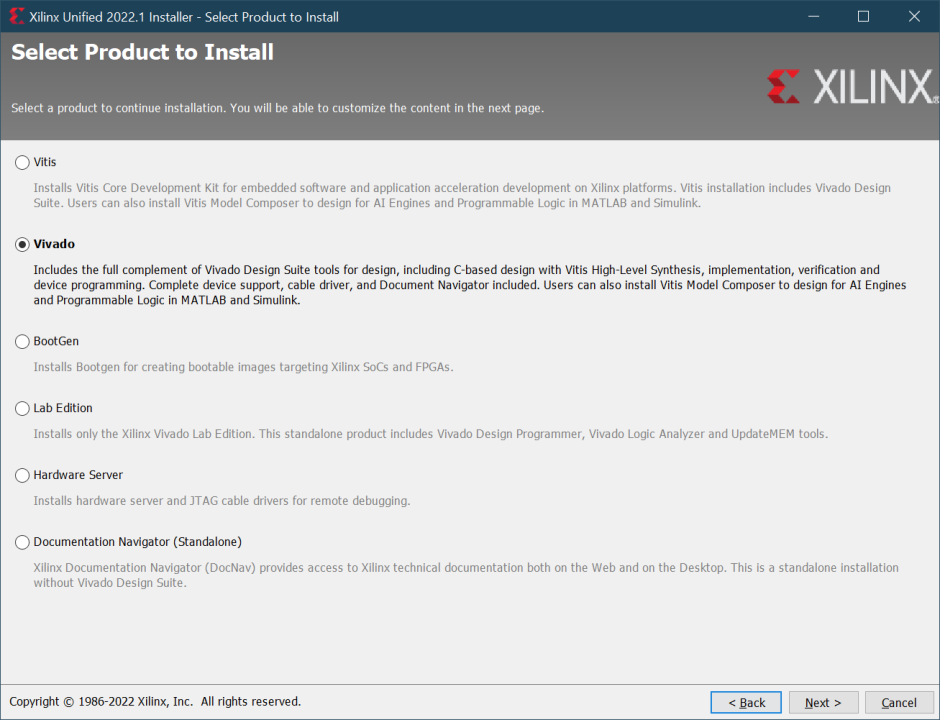

Tool Installation

So a good place to start is Vivado as it includes simulation and synthesis under one product. But Vivado's Xsim is "entry level". ModelSim was perhaps the industry standard 15-20 years ago the smaller brother of QuestaSim which is their professional edition. At home I use the ModelSim that comes free with Quartus Prime Lite because of familiarity. It is crippled in design size, and goes slowly after using too many VHDL statements, but I still find it works well for trying out ideas.

- Vivado Webpack latest edition

- The Webpack is now just the same as Standard et al, only without a license you have fewer devices available. So use the unified installer, and install off the Internet as opposed to downloading the full installer (@ 70GB+)

- Intel Quartus Prime Lite Ver 20.1.1. If you only need the VHDL simulator, click the "Individual Files" tab and select the download for ModelSim. Otherwise download both Quartus Prime light and ModelSim from the "Multiple Files" tab (or individually). Since Ver 21.1 you may try to download the more recent version of the simulator which has been upgraded to QuestaSim, however you will need to request a free licence. The instructions to follow are detailed at VHDL Whiz, and involve extra steps such as filling out a form for a licence request with your network card's MAC address and installing a license file. I'm sure it will be fine ;-). For the impatient, stick to ModelSim version 20.1.1, it will do well enough.

Those two downloads give you two simulators and two synthesis tools. I suggest you start with Vivado, use Xsim initially, then get clever later with ModelSim and Quartus Prime later. Modelsim is best used with a script to compile code. I have simple examples for you on GitHub.

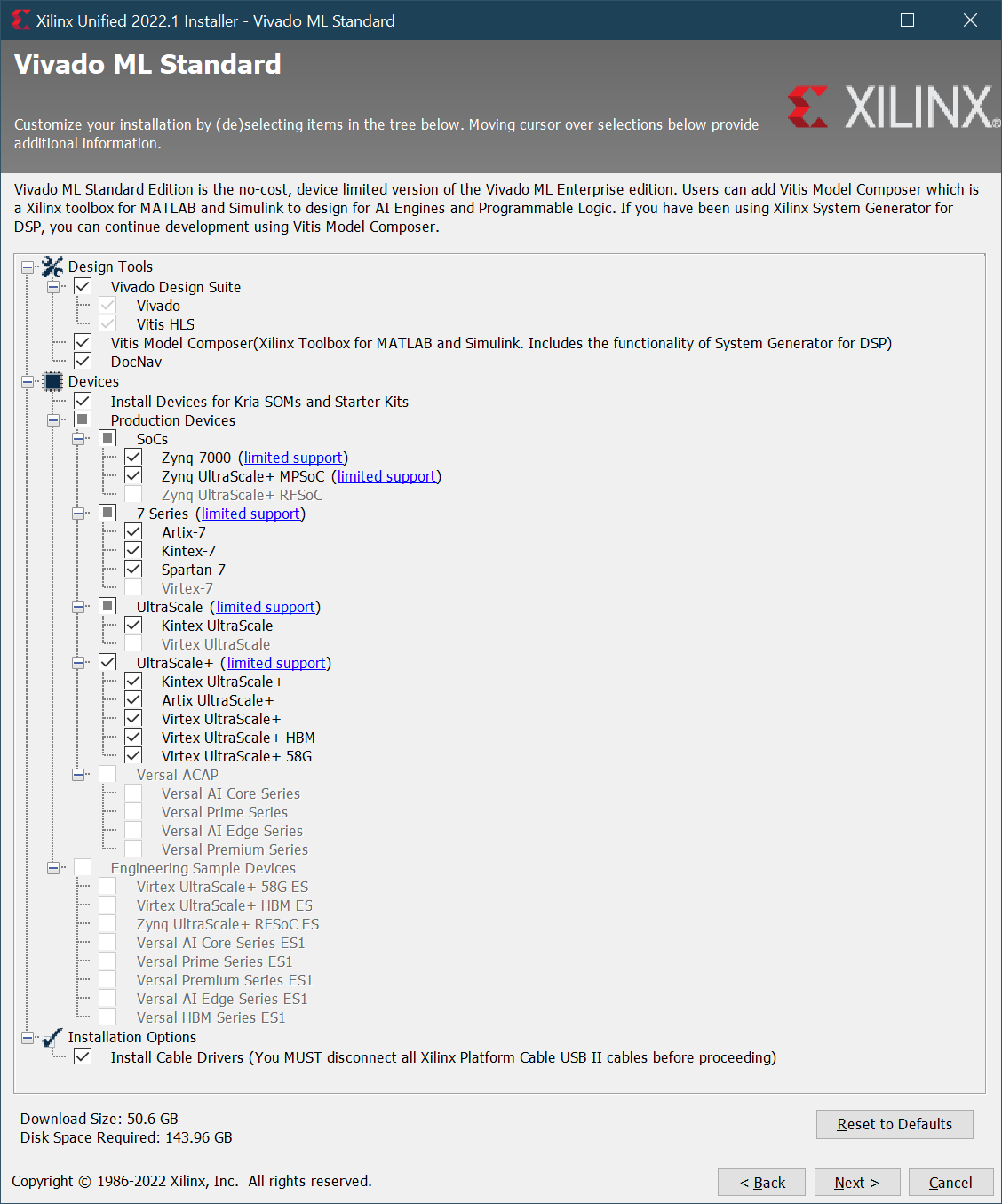

Suggested Vivado Installation Options

Learning VHDL

So all you need to do now is learn VHDL. It's not terrible, as proven by my son aged 13, working his way through some online tutorials. Here are some useful resources, and I'll grow the list as I stumble upon more.

Tutorials

- VHDL Whiz

- Nandland

- Except they are confused about state machines on their Interview Questions crib page, can't spell 'Mealy' and has people complaining about that model interview answer. I've had one person turning up to interview who was very reluctant to deviate from their script. I wonder where he got the wrong answer from? Nandland even scripted the same mistake in their YouTube video.

- TutorialsPoint

- FPGA Tutorial

- FPGA4student

- Digilent's Getting Started with VHDL: Syntax, Programming & Modules

I am familiar with the first two sites.

- The first is very good and professional, and you'll get a response from the author.

- The second is handy for type conversion hints, remember VHDL is strongly typed so their conversion quick reference is routinely handy.

- The last few popped up searching the Internet and looked good on initial inspection, there are more.

Suggested Steps

I suggest your plan of attack is:

- A "hello world" equivalent for VHDL. Perhaps an AND gate with its output registered in a single clocked process?

- Don't forget you will need a test bench for your "device" to provide stimulus and verify the results it outputs (for your "continuous integration" pipelines of the future!).

- Synthesis will then add in all sorts of I/O and asking you for a pin out at implementation, but you should get something to inspect and give you confidence in driving the tools.

- Later you might attempt "out of context" synthesis to get rid of the I/O annoyances, but at the expense of some setup. Then don't bother with implementation until you actually target a real device, remember we're keeping it simple to start with.

- Pick off something more exciting, e.g. Polynomial division, or a FIR filter.

- Then start playing with hierarchy, which is a bit annoying in VHDL (and see the attraction of block diagram editors, up until you need you source code control them). This requires you to have some ideas, but search the web for other people's ideas.

- Try using Vivado to generate an IP Core that you then stitch into your design, fixed point division following your FIR filter?

- This might annoy you if you decide to maintain your source outside of Vivado and not to be tied to the way the tool wants you to work, so you need to figure out how to manage your source code along side generating IP.

- Try your code out in ModelSim

- Use my compilation scripts on GitHub as a template.

- Try your code out in Quartus (obviously without any Xilinx specific IP Cores...).

- Just see how different the tools feel.